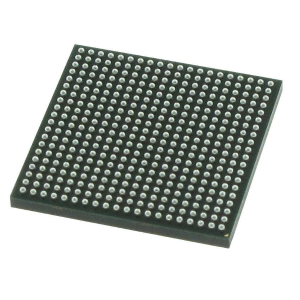

LCMXO1200C-3TN144I FPGA – Array ta' Bieb Programmabbli fil-Post 1200 LUTs 113 IO 1.8 /2.5/3.3V -3 Spd I

♠ Deskrizzjoni tal-Prodott

| Attribut tal-Prodott | Valur tal-Attribut |

| Manifattur: | Kannizzata |

| Kategorija tal-Prodott: | FPGA - Array ta' Bieb Programmabbli fil-Post |

| RoHS: | Dettalji |

| Serje: | LCMXO1200C |

| Numru ta' Elementi Loġiċi: | 1200 LE |

| Numru ta' I/Os: | 113 I/O |

| Vultaġġ tal-Provvista - Min: | 1.71 V |

| Vultaġġ tal-Provvista - Massimu: | 3.465 V |

| Temperatura Minima tat-Tħaddim: | - 40°C |

| Temperatura Massima tat-Tħaddim: | + 100°C |

| Rata tad-Data: | - |

| Numru ta' Trasmettituri: | - |

| Stil ta' Immuntar: | SMD/SMT |

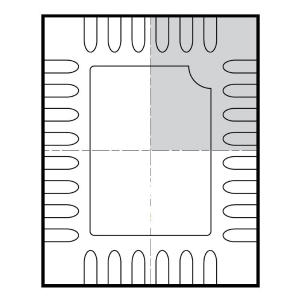

| Pakkett/Kaxxa: | TQFP-144 |

| Ippakkjar: | Trej |

| Marka: | Kannizzata |

| RAM Distribwita: | 6.4 kbit |

| RAM tal-Blokk Inkorporata - EBR: | 9.2 kbit |

| Għoli: | 1.4 mm |

| Tul: | 20 mm |

| Frekwenza Massima tat-Tħaddim: | 500 MHz |

| Sensittiv għall-Umdità: | Iva |

| Numru ta' Blokki ta' Array Loġiċi - LABs: | 150 LAB |

| Kurrent tal-Provvista Operattiva: | 21 mA |

| Vultaġġ tal-Provvista tat-Tħaddim: | 1.8 V/2.5 V/3.3 V |

| Tip ta' Prodott: | FPGA - Array ta' Bieb Programmabbli fil-Post |

| Kwantità tal-Pakkett tal-Fabbrika: | 60 |

| Sottokategorija: | Ċirkwiti Integrati tal-Loġika Programmabbli |

| Memorja Totali: | 15.6 kbit |

| Wisa': | 20 mm |

| Piż tal-Unità: | 1.319 gramma |

Mhux volatili, Infinitament Rikonfigurabbli

• Instant-on – jixgħel f'mikrosekondi

• Ċippa waħda, l-ebda memorja ta' konfigurazzjoni esterna meħtieġa

• Sigurtà tad-disinn eċċellenti, l-ebda bit stream biex jiġi interċettat

• Ikkonfigura mill-ġdid il-loġika bbażata fuq l-SRAM f'millisekondi

• SRAM u memorja mhux volatili programmabbli permezz tal-port JTAG

• Jappoġġja l-ipprogrammar fl-isfond ta' memorja mhux volatili

Modalità ta' Rqad

• Jippermetti tnaqqis fil-kurrent statiku sa 100x

Rikonfigurazzjoni tat-TransFR™ (TFR)

• Aġġornament tal-loġika fil-qasam waqt li s-sistema tkun qed topera

Densità Loġika ta' I/O Għolja

• 256 sa 2280 LUT4s

• 73 sa 271 I/O b'għażliet estensivi ta' pakketti

• Migrazzjoni tad-densità appoġġjata

• Imballaġġ mingħajr ċomb/konformi mar-RoHS

Memorja Inkorporata u Distribwita

• Sa 27.6 Kbits sysMEM™ RAM tal-Blokk Inkorporata

• RAM distribwita sa 7.7 Kbits

• Loġika ta' kontroll FIFO dedikata

Buffer I/O Flessibbli

• Il-buffer sysIO™ programmabbli jappoġġja firxa wiesgħa ta' interfejsijiet:

– LVCMOS 3.3/2.5/1.8/1.5/1.2

– LVTTL

– PCI

– LVDS, Bus-LVDS, LVPECL, RSDS

PLLs tas-sysCLOCK™

• Sa żewġ PLLs analogi għal kull apparat

• Multiplikazzjoni, diviżjoni, u bidla fil-fażi tal-arloġġ

Appoġġ fil-Livell tas-Sistema

• Skennjar tal-Konfini tal-Istandard IEEE 1149.1

• Oxxillatur abbord

• L-apparati jaħdmu b'provvista tal-enerġija ta' 3.3V, 2.5V, 1.8V jew 1.2V

• Programmazzjoni fis-sistema konformi mal-IEEE 1532